증착 공정 변수에 대해서 설명을 해드리겠습니다.

증착 공정 변수

1. Uniformity

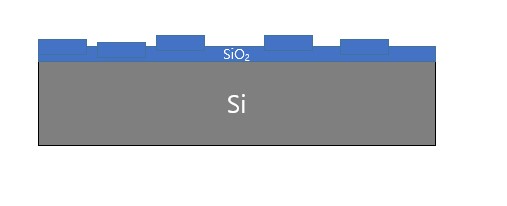

Wafer 전체에 일정한 두께로 Target material이 증착되어 있는가 에 대한 지표입니다.

Uniformity가 좋지 않으면, 개별 칩 간 Vth 등의 특성 차이가 날 수 있습니다.

위 사진의 SiO2 층이 gate oxide면 소자 간 gate oxide 두께가 매우 다르겠죠.

얇으면 터널링이 일어날 수 있고, 너무 두꺼우면 유전 효과가 느려 소자 자체도 느려질 것입니다.

식각에서도 과식각/식각 x 문제로 인하여 후공정에서 오염물질로 작용할 수 있습니다.

2. Step coverage

Uniformity가 얼마나 좋냐?를 객관적으로 나타내는 수치입니다.

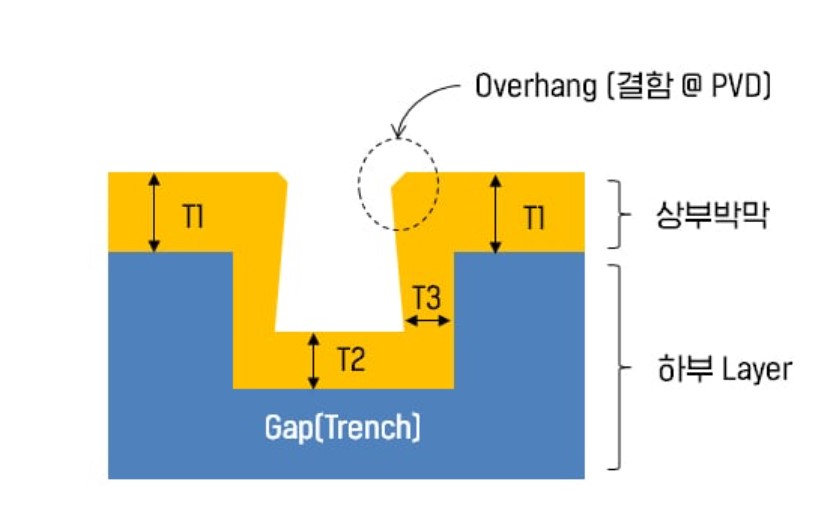

반도체의 특정 막은 금속 등으로 하부 소자와 상부 소자를 연결하기 위해 아래 그림과 같이 뚫려있습니다. Etch 공정으로 hole, via를 생성하지요.

Step Coverage가 진행되었는지를 보기 위해 정상적인 막 두께(T1) 대비 갭 밑면(T2)과 옆면의 두께(T3)를 비율로 나타내며, 이를 각각 Bottom Step Coverage(T2/T1), Side Step Coverage(T3/T1)라 부릅니다. [1]

Step coverage가 높을수록 wafer 표면의 모든 면이 일정한 두께로 잘 증착된 것으로 판단합니다.

3. Aspect ratio

위의 사진에서, 높이/폭의 값을 수치화한 것을 Aspect ratio, 종횡비라고 합니다.

즉, 값이 높을수록 높이가 길고 폭이 좁습니다. 종횡비가 클수록 공정 난이도가 매우 올라가지요.

4. Adhersion

Target material과의 접착력을 측정하는 것입니다.

접착력이 좋지 않다면, 박막이 떨어져 나가게 됩니다.

5. Mean Free Path

MFP는 분자가 다른 분자와 충돌하지 않고 이동할 수 있는 평균 거리를 의미합니다.

MFP가 높을수록 표면에 도달하는 원자의 에너지가 높아 기판의 빈자리를 잘 찾아가기 때문에 uniformity, step coverage가 좋아집니다.

증착 3대 조건

1. Good filling of Spaces

반도체의 집적도가 매우 높아졌기 때문에 Via, Hole의 Aspect ratio는 매우 커졌습니다.

이로 인해 Via, hole을 금속 물질로 꽉꽉 채우는 것이 어려워졌죠.

2. Good uniformity & step coverage

이 부분은 앞서 설명해 드렸습니다.

3. Good composition with good electric properties

원하는 전기적 특성을 갖게 하기 위해 원자들의 조성비를 연구를 해야 합니다.

증착 문제

공정이 미세화됨에 따라 문제가 생겼습니다.

1. Step coverage issue

Metal의 step coverage가 좋지 않으면, 얇게 증착된 부분이 Hot carrier effect로 인해 단선될 위험이 있습니다.

2. Filling issue

내부 공간을 제대로 채우지 못하여 내부 공간 사이에 큰 구멍, 즉 Void가 형성되게 되고, 이를 통해 단선이 될 위험이 있습니다.

참고 자료 :

[1] https://news.skhynix.co.kr/post/ald-using-atoms

'반도체 8대 공정 > 5. Deposition' 카테고리의 다른 글

| 5.6 증착 공정) 반도체 증착 장비 진공 잡는 법(feat. Sputter 장비 작동법) (0) | 2022.12.15 |

|---|---|

| 5.5) PVD의 이해 (0) | 2022.12.11 |

| 5.3 증착 공정) CVD 장비 종류, 각 장비 장단점 (0) | 2022.12.08 |

| 5.2 증착 공정) CVD의 이해(CVD의 모든 것) (0) | 2022.11.30 |

| 5.1 증착 공정) 박막 증착 Mechanism (박막 성장 기구 6가지) (1) | 2022.11.29 |

댓글