이번 장에서는 이번 카테고리의 마지막, MOSFET에 대해서 설명을 해드리겠습니다.

전자기기는 대부분 MOSFET이 사용됩니다.

<BJT 관련 내용은 쓰이지 않은 소자이고, 면접에서 나오지 않은 주제이므로 생략하겠습니다.>

다중 접합 소자, MOSFET이란?

pn junction은 단일 접합 소자(두 개의 반도체 접합)로 스위칭 특성 및 정류 특성을 이용합니다.

MOSFET는 트랜지스터로, 단일 접합 소자가 아닌 다중 접합 소자입니다.

트랜지스터는 스위칭 특성 및 전류 이득, 전압 이득, 신호 전력 이득 등 증폭기 특성을 얻기 위해 사용합니다.

MOSFET의 종류

n-channel MOSFET(nMOS) : 채널에서 전하를 움직이는 캐리어가 전자인 트랜지스터입니다.

p-channel MOSFET(pMOS) : 채널에서 전하를 움직이는 캐리어가 정공인 트랜지스터입니다.

CMOS : n-channel MOSFET과 p-channel MOSFET이 합쳐진 소자입니다.

MOSFET은 Metal Oxide Semiconductor Field Effect Transistor의 약자로, 말 그대로 Metal, Oxide, Semiconductor로 구성되어 있습니다.

MOSFET의 작동 원리(nMOS 기준)

먼저 그림을 보여드리고 설명해 드리겠습니다.

Gate에 적당한 크기의 (+) 전압을 걸어주면, Oxide의 유전 분극 특성으로 인해 반도체 표면에 소수 캐리어인 전자가 모이게 됩니다.

n+로 고도핑되어 전자가 엄청 많은 source, drain 부분과 연결되게 되죠. 이 연결되는 통로를 '채널'이라고 합니다. 이 채널을 통해 전자가 이동하죠.

반대로 Gate에 (-) 전압을 걸어주면, Oxide의 유전 분극 특성으로 인해 반도체 표면에 다수 캐리어인 정공이 모이게 됩니다.

n+로 고도핑되어 전자가 엄청 많은 source, drain 부분 사이에 정공이 엄청 많아집니다.

즉, 채널이 형성되지 않아 전자가 이동을 할 수 없습니다.

<이런 이론까지 꼭 알고 가셔야, 대기업 면접에서 살아남으실 수 있습니다. nMOS, pMOS 원리에 대해서 안 물어보는 기업이 없습니다.>

이제, 반도체공학자로서 에너지 밴드를 설명해드리겠습니다.

MOS 구조의 Energy Band과 게이트 문턱 전압

MOSFET 그림에서 source, drain을 제외한 MOS 구조에 대해서 설명을 해드리겠습니다.

MOS 구조는 일종의 Capacitor입니다.

도핑한 semiconductor은 전기적 성질을 가지고 있기 때문에 Capacitor의 전극 역할이 가능합니다.

1. p형 반도체 MOS Cap에서 metal에 (-) 전압을 가하면?

p 반도체 관련 입장에서 + 전압에 따라 전기장이 위쪽으로 형성이 되어 다수 캐리어인 정공이 반도체 위 쪽으로 이동을 하게 됩니다.

유전체 입장에서는 전극에 - 전압이 인가됨에 따라 유전 분극 효과를 통해 반도체 위 쪽에 정공이 이동하게 되죠.

결론적으로, 반도체 윗부분에 정공이 축적되게 됩니다.

2. p형 반도체 MOS Cap에서 metal에 (+) 전압을 가하면?

위와 마찬가지 이유로 p형 입장, 유전체 입장에서 반도체 윗부분에 정공이 없어지게 됩니다.

이에 따라 다수 캐리어인 정공이 공핍된 공핍층이 형성되게 됩니다.

이 개념을 에너지 밴드로 설명을 해드리겠습니다.

만약, 역방향 바이어스를 크게 걸어주게 되면 어떻게 될까요?

p형 반도체에서 reverse bias를 크게 가하게 되면, 반도체 표면이 n-type로 반전됩니다.

이게 MOSFET 단원 중 가장 알아야 할 핵심 내용입니다. 반전이 되는 전압이 게이트 문턱 전압이니까요.

Inversion layer가 곧 channel이라고 생각하시면 됩니다.

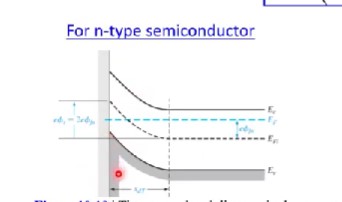

n-type 반도체는 다음과 같습니다.

결론적으로, 반도체에 reverse voltage를 가해주게 되면 inversion layer가 형성됨을 알 수 있습니다.

이제 식을 규명하겠습니다.

p형 반도체 계면에 역방향 바이어스를 가하면, 다수 캐리어의 정공이 전계 쪽으로 달려가서 없어져 계면 부분에 음으로 대전된 어셉터 이온이 남게 됩니다. 이 음이온이 있는 부분까지를 공간 전하 폭이라고 하죠.

파이 fp는 페르미 에너지에서 진성 페르미 에너지 레벨을 뺀 값입니다.

banding 된 정도를 파이 s라고 정의를 내렸습니다.

즉, bulk와 surface에서 측정된 Efi 측정값의 차이이죠.

만약 이 밴딩이 심해져서 2파이 fp가 되면 문턱 반전점이 됩니다.

소수 캐리어가 축적이 되기 시작하는 거죠.

이때의 전압을 문턱전압이라고 합니다.

n- type semiconductor일 때입니다.

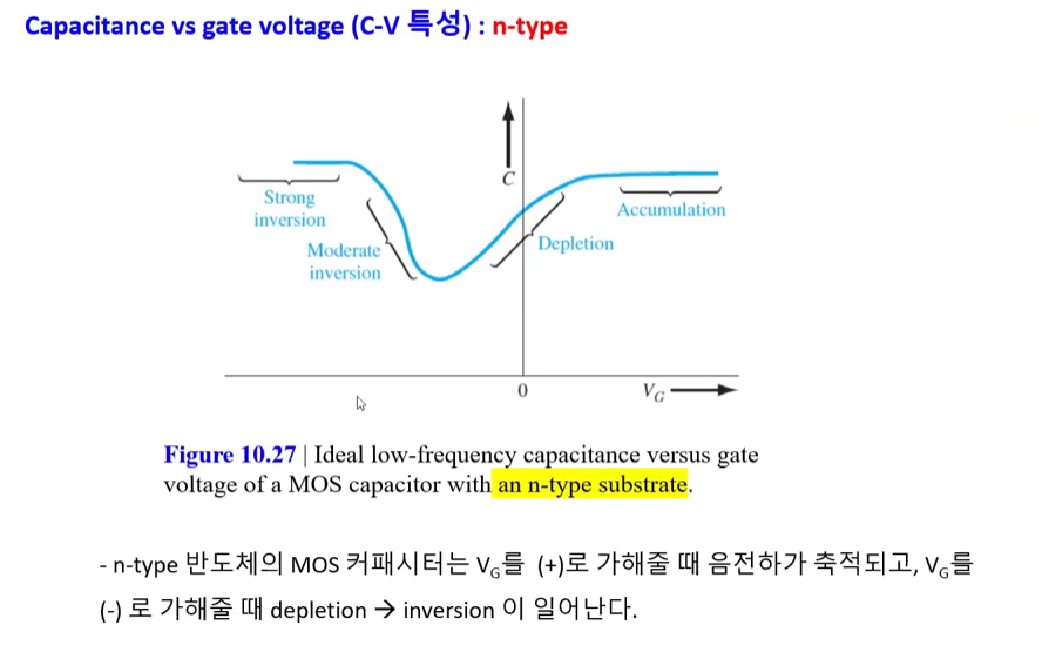

MOS Capacitor operationg conditions

MOS Capacitor의 3가지 operationg conditions가 있습니다.

축적, 공핍, 반전입니다.

1. 축적일 때

순방향으로 반도체에 전압을 가해주게 되면 다수 캐리어가 계면에 축적되는 것을 말합니다.

2. 공핍일 때

역방향으로 반도체에 전압을 가해주게 되면 공핍층이 생깁니다.

3. 반전일 때

더 센 역방향으로 반도체에 전압을 가해주게 되면 반전층이 생깁니다.

전체를 종합한 C-V 특성입니다.

'반도체 공학 > 반도체 소자 이론' 카테고리의 다른 글

| 무어의 법칙, 반도체 개발 속도의 Guideline을 제공하다. (Feat. 3 나노 공정에서 3나노가 뭘 의미해?) (0) | 2023.01.10 |

|---|---|

| 반도체 물성과 소자) 12. MOSFET (0) | 2022.10.29 |

| 반도체 물성과 소자) 10. 반도체 Heterojunction (0) | 2022.10.27 |

| 반도체 물성과 소자) 9. Metal Semiconductor Heterojunction (0) | 2022.10.26 |

| 반도체 물성과 소자) 8. PN junction (Energy band 그림) (1) | 2022.10.25 |

댓글